The circuit is almost ready to go to layout again. This week I took a close look at the schematic design to look for errors and unfinished tasks. By the way, you can put notes on a schematic to help you find anything you put off for later.

I have received the PCBs for my client, but I haven’t had the chance to populate the first one yet. This means I haven’t had a chance to test the charging circuit yet. The availability of inexpensive PCB fabrication like OSH park has made a mini PCB test run reasonably priced. You can now design a development board that exactly meets your requirements very inexpensively. Since each iteration of the this design isn’t costing a lot, I am testing multiple changes each time. This allows me to work with devices that I am completely inexperienced at very low risk.

I started with the lithium cell charging circuit. I verified the input from the micro USB connector is tied to the input of the management chip. I copied the timing and current limit device values from my client’s design. The lithium cell (connector) is connected to GND and the dedicated pin on the management chip. The status outputs are tied to LEDs so I have some indication of what is happening during charging. I may try to incorporate these signals later in the design. The system power output is connected to the 3.3V regulator which is working well on the two test boards I have already built.

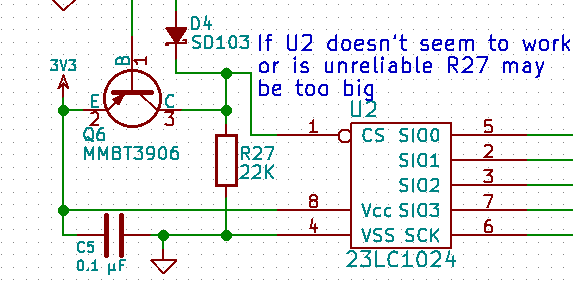

Next I looked at the SPI RAM Chip select logic. The transistor Q6 turns on when CS0 is low; this pulls the chip select line for U2 high preventing U2 from contending with the SPI bus when the flash chip is being accessed. There is a diode blocking the high from pulling GPIO15 high during reset. There is a pull down resistor for when GPIO15 is low and CS0 is high to activate U2 chip select. This is untested but the design looks like it will work. I chose 22K resistors for the pulldowns on GPIO15 and U2 chip select as a balance between current required when GPIO15 is high and the speed at which U2 chip select will fall when released. Since I don’t know the amount of capacitance of that circuit, I may have to change that resistor value later. Good place to put a note on the schematic.

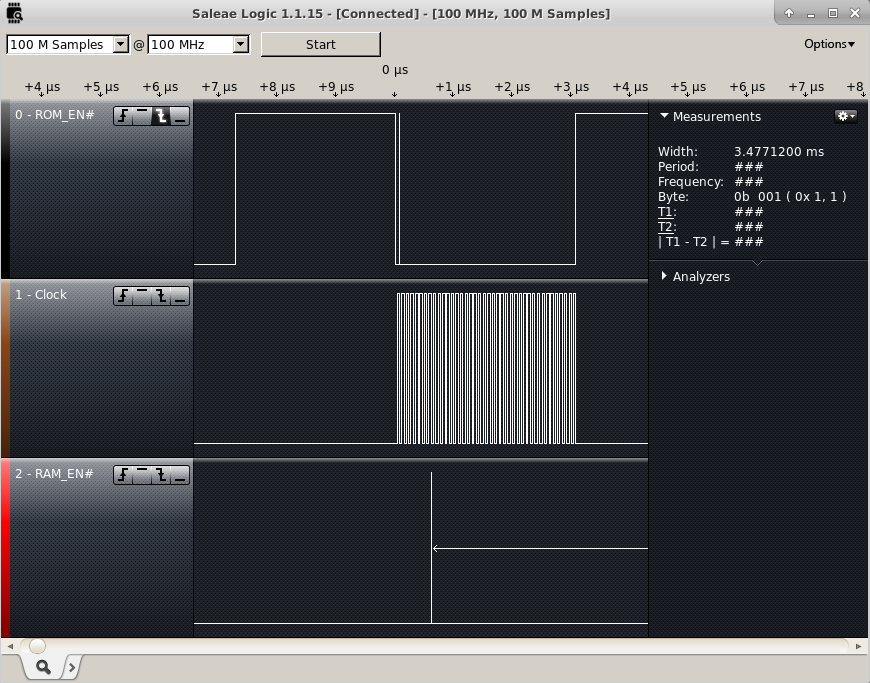

The level shifter U3 is untested, I should test it before I go to layout. Another note.

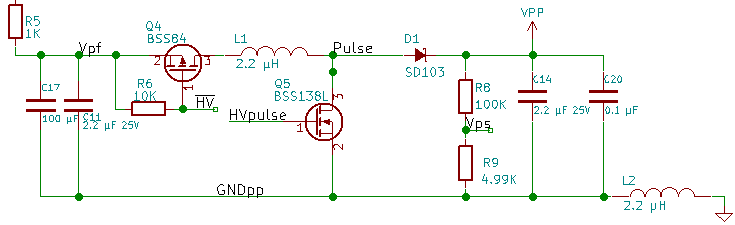

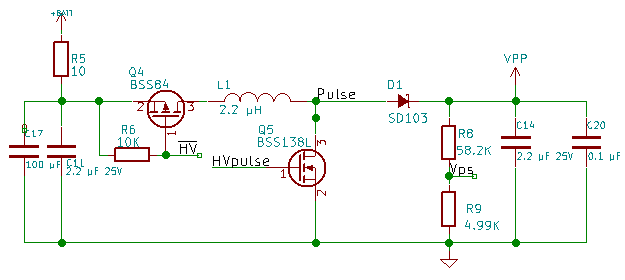

I decided earlier that the voltage booster was working but needs to have an isolated ground on the PCB layout. I have added an inductor between the boost GND and the system GND. This allows for some experimentation. I can just bridge the pads with solder, I can put a resistor in there, or I can install the inductor. If isolating the GND is enough, that’s great. The resistor would help provide better filtering but could cause problems. The inductor is best filtering but will slow down signal transitions of the high voltage. I also gave the net name GNDpp to the isolated GND.

The transistor driver for VPP is untested, because I haven’t had the positive voltage available. I could have attached a 12 volt source and tested it but it’s a simple circuit. It should work. The analog switch is working, nothing to review with it.

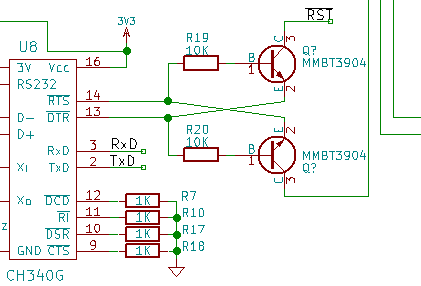

Finally, the programming control pins RST and GPIO0. I am not happy with the resistor connections. I have decided to copy the design from the NodeMCU dev board. It is simple and works well on the dev board. The only thing I am concerned about here is how much current the UART bridge pulls when not connected to USB.

Use the GitHub link to get a current copy of this design. After testing, I will go to layout.

I would love to hear any questions or suggestions. If you would do this differently, please comment.