Design reviews should be done often, at least just before a new design goes to fabrication.

During testing I had wished for some test pins at the edge of the PCB for verification. I want to add and label test pins for Reset, Txd, Rxd, 3.3V, SCK, MOSI, MISO, IO2, IO3 and L1 pulse.

I added these testpoints to the schematic along with a ground that’s easy to get to. I am putting them into a through hole 1×12 connector. I moved P1 test into the same header. In layout, I’ll place this connector next to the edge where I can get a clip lead connected for testing.

USB to Uart chip completely changed, copied reference design from NodeMCU design. It’s helpful to look at a second design for a sanity check. Everything matches up to an Arduino clone schematic found on the web. I had left DCD, RI, DSR, and CTS unconnected. Leaving inputs unconnected can cause problems. These connections may have internal pullups/pulldowns but I couldn’t find any reference to that in the datasheet. Each of these lines indicates data is ready to flow when held low, I put pulldowns on each of them.

I had changed the SPI connections to correct the mistakes I had made earlier, I have gone back to verify these connections and found conflicting information. I traced the gerber image I had found to get the pinout I currently have. If it’s not correct, I will have the test pins to help me figure out the correct pinout.

I had replace the port expander with a shift register still using the SPI to fill the register. According to the datasheet, the data shifted in will be latched on the rising edge of the RCLK pin. If I treat RCLK as a Chip Select Pin on the SPI, a one byte write will set all of the outputs very quickly. This appears that it will work well.

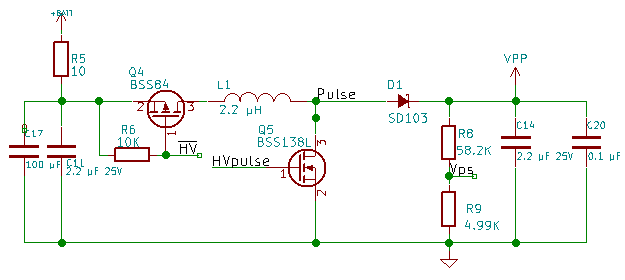

The VPP circuit changes are a big gamble. I don’t know if it will work. I am adding a 0.1 µF capacitor to the output to reduce output noise. I am adding a 10 Ohm resistor and a 100 µF capacitor to filter noise from getting back into the rest of the system. I need to isolate the ground of the high voltage circuit to only connect to regular GND Net at only 1 place on the layout. This will help reduce noise transfer back into the rest of the system. The design update is on GitHub, use the link in the upper right hand of the page.