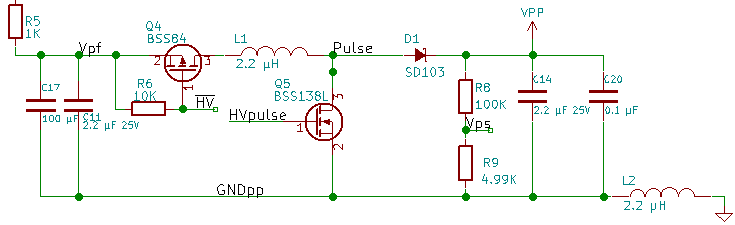

I tested the battery charging circuit this week. It failed. The lithium cell would charge, but when I disconnected the power adaptor everything shut down. I didn’t understand how the enable lines worked. In my hurry, I missed an example circuit in the datasheet that closely matched my needs. Most importantly it showed where to connect the enable lines for “normal” operation.

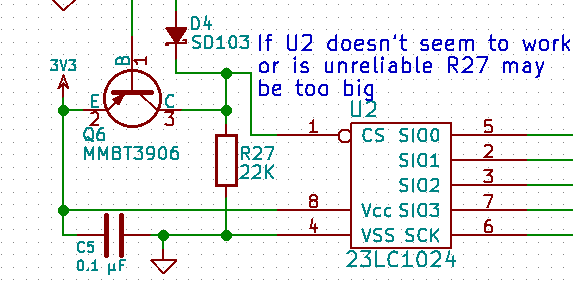

So for my client, I connected a diode from the out line of the chip to the in line of the chip(where the enables were connected to). The diode makes sure the out line is controlled by the chip and it can manage the current correctly. Note D5 in the schematic below.

This works but it is kind of a hack. Hacks are great for testing prototypes, doing one off designs, and temporary changes. Hacks lead to problems in production, if at all possible hacks should be avoided on production runs. The right way to connect this circuit for both the programmer and my client is to connect EN and ENO to the +5V rail and ENBAT to the battery positive terminal. This configuration means that anytime power is connected to the power, it will supply system voltage from the +5V supply and charge the lithium cell with whatever current is left from the 450 ma I limited it to. When the +5V rail is not powered, or under powered,the lithium cell supplies current to system.

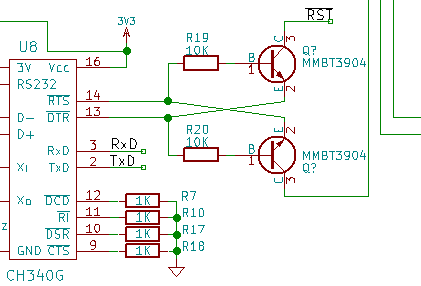

I modified the code to connect the sigma delta to GPIO13 to drive the level shifter signal, then connected 5 Volts to the Vt and measured the waveform on the pad that corresponds with GPIO 13 through the level shifter. It didn’t work, Or the DSO138 oscilloscope can’t read the sigma delta signals. I found a recommended power up sequence of the the level translator chip that I hadn’t considered before, the /OE pin should be brought low after power up. This is to prevent excessive currents, I shouldn’t get the results I am seeing, I decided to try just toggling the GPIO12, 13, 14 pins controlled by the serial communications. The system has gotten very unstable, I decided to re-flash the user config and wifi calibration data. Turned out that Vt was/is shorted to ground, My best guess is the Pad directly under the chip solder bridged to the Vt(Vccb) pin of the level shifter chip. Time to lay out again.

Do you have any Ideas or suggestions that might be useful for this design? Would you do anything differently?