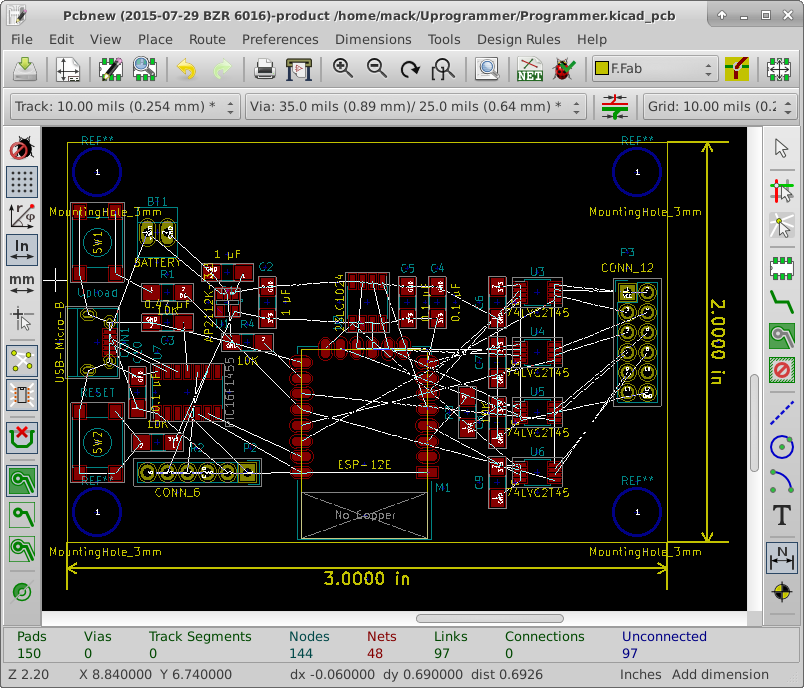

I did the routing this week. I set up the minimum trace width and separation as specified on OSHpark’s website. White lines show the connections I still needed to make, this is called the ratsnest. When the ratsnest is completely gone, I knew I was finished with the routing.

I started by placing routes on the left side of the board and then working towards the right avoiding power and ground pins. As I worked, I noticed some of the parts did not line up well for routing so I moved some footprints around the board.

About 2/3rds done I found the interactive router feature. If I switched to OpenGL mode, the interactive router became active. This router saved me a lot of time compared to the first part of the layout.

Once I finished routing everything except power and ground, I set up a pour area for ground on the back side of the board. To pour, I had to define a zone on the backside of the board. I kept this zone at least 15 thousandths from the edge of the PCB to make sure it worked with OSHPark. I also created an area around the antenna on the ESP12e that has no pour to meet their layout requirements.

To finish a pour, I had to right click on the edge of the created zone, mouse over the zone menu item and then select fill zone. I connected the surface mount parts to ground by connecting a trace to the SMT pad and then placing a via to connect to the ground plane. I finished the layout by connecting the positive voltage supply traces. I then filled the ground plane zone again to clean up any adjustments I made to tracks on the board.